半导体热门

紫光集团重组尘埃落定!赵伟国退场,前中芯国际高管接棒

紫光集团重组尘埃落定!赵伟国退场,前中芯国际高管接棒

吉莱微创业板IPO获受理!研发投入不足,募资8亿扩增高端IGBT模块等产能

吉莱微创业板IPO获受理!研发投入不足,募资8亿扩增高端IGBT模块等产能

半导体:苦日子准备开始!

半导体:苦日子准备开始!

今天来谈谈系统级封装SiP技术

今天来谈谈系统级封装SiP技术

半导体不景气

半导体不景气

源杰半导体本周上会:2021年营收超2亿,华为旗下哈勃投资为其股东

源杰半导体本周上会:2021年营收超2亿,华为旗下哈勃投资为其股东

这个产业让韩国向日本“低头”,中国也会重蹈覆辙

这个产业让韩国向日本“低头”,中国也会重蹈覆辙

推荐资讯

让区块链变成人人可用的工具,上海原创Web3.0操作系统是如何诞生的

让区块链变成人人可用的工具,上海原创Web3.0操作系统是如何诞生的

隐私之变|自我主张时代变革,从构建WEB3.0的ID体系开始

隐私之变|自我主张时代变革,从构建WEB3.0的ID体系开始

被投资圈盯上,风头超过元宇宙,Web3.0到底是啥?

被投资圈盯上,风头超过元宇宙,Web3.0到底是啥?

Web3.0,勾勒下一代互联网模样

Web3.0,勾勒下一代互联网模样

为什么说中国汽车产业已经真正“支棱”起来了

为什么说中国汽车产业已经真正“支棱”起来了

我在新能源汽车行业打工10年:从月薪2千涨至年薪40万,终于熬出头

我在新能源汽车行业打工10年:从月薪2千涨至年薪40万,终于熬出头

对话梅宏院士:数字化转型不是想不想,而是必须转

对话梅宏院士:数字化转型不是想不想,而是必须转

王兴继续“电商零售梦”:告别社区团购 美团优选变身明日达超市

王兴继续“电商零售梦”:告别社区团购 美团优选变身明日达超市

今天来谈谈系统级封装SiP技术

SiP是半导体封装领域的最高端的一种新型封装技术,将一个或多个IC芯片及被动元件整合在一个封装中,综合了现有的芯核资源和半导体生产工艺的优势。SiP是为整机系统小型化的需要,提高半导体功能和密度而发展起来的。 SiP使用成熟的组装和互连技术,把各种集成电路如CMOS电路、GaAs电路、SiGe电路或者光电子器件、MEMS器件以及各类无源元件如电阻、电容、电感等集成到一个封装体内。

自从1960年代以来,集成电路的封装形式经历了从双列直插、四周扁平封装、焊球阵列封装和圆片级封装、芯片尺寸封装等阶段。而小型化、轻量化、高性能、多功能、高可靠性和低成本的电子产品的总体发展趋势使得单一芯片上的晶体管数目不再是面临的主要挑战,而是要发展更先进的封装及时来满足产品轻、薄、短、小以及与系统整合的需求,这也使得在独立的系统(芯片或者模块)内充分实现芯片的功能成为需要克服的障碍。

这样的背景是SiP逐渐成为近年来集成电路研发机构和半导体厂商的重点研究对象。 SiP作为一种全新的集成方法和封装技术,具有一系列独特的技术优势,满足了当今电子产品更轻、更小和更薄的发展需求,在微电子领域具有广阔的应用市场和发展前景。

S iP/SoP

近年来,随着消费类电子产品(尤其是移动通信电子产品)的飞速发展,使得三维高密度系统级封装(3D SiP,System in Package/SoP,System on Package)成为了实现高性能、低功耗、小型化、异质工艺集成、低成本的系统集成电子产品的重要技术方案,国际半导体技术路线(ITRS)已经明确SiP/SoP将是未来超越摩尔(More than Moore)定律的主要技术。

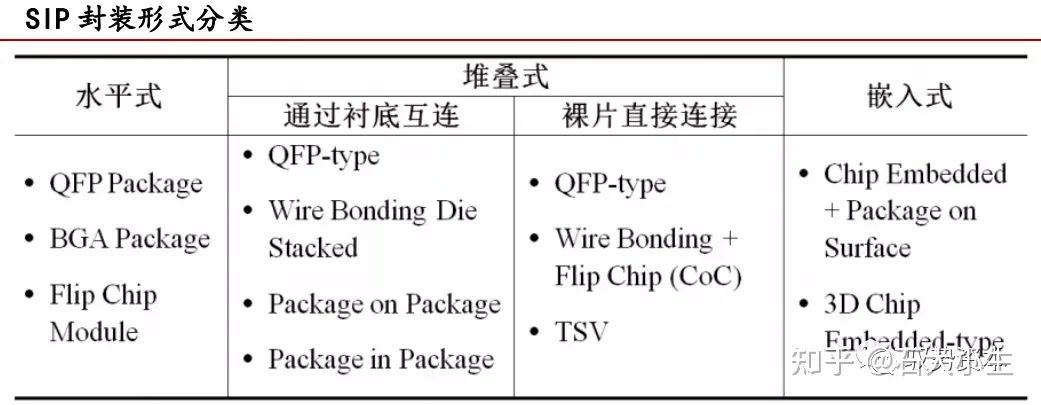

SiP从结构方向上可以分为两类基本的形式,一类是多块芯片平面排布的二维封装结构(2D SiP),另一类是芯片垂直叠装的三维封装/集成结构(3D SiP)。

在2DSiP结构中,芯片并排水平贴装在基板上的,贴装不受芯片尺寸大小的限制,工艺相对简单和成熟,但其封装面积相应地比较大,封装效率比较低。

3DSiP可实现较高的封装效率,能最大限度地发挥SiP的技术优势,是实现系统集成的最为有效的技术途径,实际上涉及多种先进的封装技术,包括封装堆叠(PoP)、芯片堆叠(CoC)、硅通孔(TSV)、埋入式基板(Embedded Substrate)等,也涉及引线键合、倒装芯片、微凸点等其他封装工艺。

3DSiP的基本概念正是将可能实现的多种功能集成于一个系统中,包括微处理器、存储器、模拟电路、电源转化模块、光电器件等,还可能将散热通道等部件也集成在封装中,最大程度的体现SiP的技术优势。

系统级封装技术可以解决目前我们遇到的很多问题,其优势也是越来越明显,如产品设计的小型化、功能丰富化、产品可靠性等,产品制造也越来越极致,尤为重要的是,提高了生产效率,并大幅降低了生产成本。

当然,难点也是存在的,系统级封装的实现,需要各节点所有技术,而不是某一技术所能实现的,这对封装企业来说,就需要有足够的封装技术积累及可靠的封装平台支撑,如高密度模组技术、晶圆级封装技术等。

免责声明* 本文内容源于《知乎:石大小生》仅是为了交流和学习,内容如有侵权或 失误失实,敬请读者不吝赐教批评指正或者联系平台处理。本平台拥有对此声明的最终解释权。

更多相关内容

-

拟上市公司股权结构的建议

股权是多种股东权利的集合体(投票权、分红权、知情权、经营决策权、选举权、优先受让权、优先认购权、转...

-

【Brain】为什么有的人很聪明,大脑结构有什么不一样吗

@ Giordano Poloni 上世纪八十年代,有研究发现,智商越高的人,在处理认知任务时,大脑皮层能量代...

-

26.1万栋经营性自建房存在安全隐患!检测鉴定人才缺口大,学习1个月,做懂鉴定的结构人!

7月8日,全国自建房安全专项整治工作推进现场会在浙江省杭州市召开。会议指出,各地区、各部门高度重视...

-

后续政策市场影响几何

央行周一公布数据显示,6月份人民币贷款2.81万亿元,社会融资规模增量5.17万亿元,广义货币(M2)余额同比...

-

3D图纸 非标设备 免费下载

图纸软件:Solidworks 图纸版本:2018 文件大小:62.76MB 下载方式:免费下载 移动式挖煤机,不仅...

-

思考结构,决定了你能看多远

来源/笔记侠 大家会发现身边一定有这样的同事,跟你说件事咿咿呀呀说半天,你也不知道他到底想表达...

-

便利店单品管理和超市品类管理有什么区别

每个单品都需要创造最大价值,便利店更加注重单品管理。超市追求品类齐全一次性满足消费需求,而又通过...

-

华安基金王斌:能源结构转型背景下,新能源产业前景广阔

近两年以来,能源相关资产表现较为亮眼,在过去几年“双碳”作为全球共识的前提下,不仅仅新能源发展迅...

-

守夜人司令+结构学文章合集

考虑到 懒人专属群 里司令的粉丝很多,小懒把他公众号的文章列表用python爬下来做成站点,方便群友查...

-

| 百合水上乐园

△Futuroscope 公园 Futuroscope 是一个法国著名的休闲公园,以科技、科学、希望和乐趣为主题。而LILY就...

推荐阅读